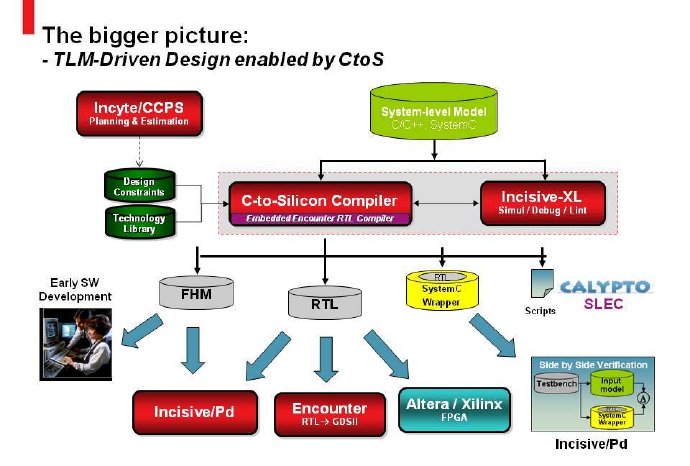

Der C-to-Silicon Compiler ist das Herzstück der nächsten Generation von TLM-basiertem (transaction-level modeling) Entwurf auf Systemebene und den Verifikationslösungen von Cadence. Die Lösung, für die sich Casio entschieden hat, kombiniert Encounter® RTL Compiler, Incisive® Enterprise Simulator und C-to-Silicon Compiler. Durch diese Kombination erhielt Casio einen leistungsfähigen, wirkungsvollen Entwurfs- und Verifikations-Flow für gemischte Control- und Datapath-Entwürfe, beginnend von SystemC bis hin zu den Logikgattern.

Die C-to-Silicon Compiler High-Level Synthese mit dem Embedded RTL Compiler ermöglichte Ingenieuren von Casio, IP mit kleinerer Fläche im Vergleich zum ursprünglichen RTL-Entwurf zu entwickeln. Außerdem konnte Casio einen nahtlosen Verifikations-Flow von SystemC bis zu RTL verwirklichen - dank Incisive Enterprise Simulator, verbunden mit der Fähigkeit des C-to-Silicon Compilers, automatisch einen SystemC Wrapper für die RTL-Verifikation zu generieren.