TestWay, Testcoverage-Tool der Referenzklasse, ermöglicht es Anwendern, die Berechnung und Analyse der Testabdeckung für eine Vielzahl industrieüblicher Inspektions- und Testsysteme durchzuführen. Dieses Tool wurde nun so erweitert, dass der Anwender den physikalischen Zugriff auf Testknoten gezielt optimieren kann und so ein Maximum an Testabdeckung erreicht.

Das interaktive, regelbasierte Programm "Probe Analyzer" unterstützt den Layout- und Test-Entwickler bei der Lokalisierung möglicher Testpunkte, die sich für die Kontaktierung mit Testnadeln eignen. Dabei werden Zahlreiche Randbedingungen berücksichtigt: Zugangsbeschränkungen, Abstandschecks und Testpunkt-Zuordnungen werden ebenso berücksichtigt, wie Verwendung maximaler Nadelgrößen, Pinraster, Agilents Bead-Probe Technologie sowie anwenderspezifische Richtlinien.

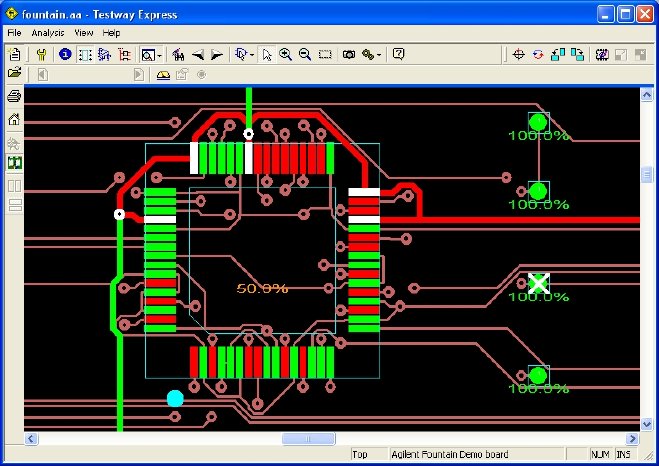

Sobald die potenzielle Platzierung der Testnadeln definiert ist, kann TestWay die Testabdeckung für In-Circuit-Tests (ICT) und Flying-Probe-Tests (FPT) anhand der Messmöglichkeiten der Ziel-Testsysteme ermitteln. "Probe Analyzer" erstellt einen umfassenden Bericht, in dem klar dargestellt wird, ob für jeden Netzknoten eine geeignete Stelle für den Testpunkt definiert wurde. Verletzungen der Regeln für die mechanische Anordnung der Testpunkte werden hervorgehoben, sodass diese Information für die Optimierung des Konstruktion oder des Layouts zur Verfügung steht. Wenn der Bericht in den Layout-Viewer eingelesen wird, werden relevante Stellen farblich hervorgehoben, sodass die nichttestbaren Netze des Designs von Layout- und Test-Entwickler grafisch einfach verfolgt werden können.

TestWay bietet ausgefeilte Testabdeckungs-Analysen. Der Anwender kann Tester-Linien definieren und ICT und FPT mit ergänzenden Technologien wie AOI, AXI, BST, MDA und Funktionstest kombinieren. Noch vor Beginn der eigentlichen Testentwicklung kann für verschiedene Teststrategien die jeweils theoretisch erreichbare Testabdeckung ermittelt werden. So werden Bereiche identifiziert, wo die Testabdeckung verbessert werden kann. Regelbasiert werden Verletzungen der DfT-Maxime erkannt, die die Effizienz des Tests limitieren.

Durch die Verknüpfung der Testabdeckungs-Abschätzung mit den mechanischen Randbedingungen des Leiterplatten-Layouts können Anwender im Vorfeld sichtbar machen, welcher Grad der Testabdeckung realistischerweise erreichbar sein wird und wie die Effizienz des fertiggestellten Tests zu bewerten ist.

"In der modernen Elektronik-Welt, wo Entwicklung und Produktion in der Verantwortung verschiedener Bereiche sind, erwarten die Märkte eine neue Generation von Werkzeugen, die von beiden Unternehmensbereichen genutzt werden können", erklärt Christophe Lotz, Geschäftsführer von ASTER Technologies. "Jetzt können Entwicklungs- und Test-Ingenieure innerhalb weniger Minuten das Fehlen von Testpunkten erkennen und die Konsequenzen in Bezug auf die Testabdeckung einschätzen."

ASTER bietet eine umfangreiche Produktpalette für elektrisches Designfor-Test (DfT) sowie die Analyse der Testabdeckung. Der Anwender kann sich daraus die Werkzeuge zusammenstellen, die seinen aktuellen Anforderungen entsprechen. TestWay ist ein hochgradig skalierbares Produkt. Es reicht von "TestWay Express" für die Berechnung und Messung der Testabdeckung bis zu "TestWay Classic" mit vollständig programmierbarer Umgebung, die kundenspezifische Regeln unterstützt, Kriterien für die Testoptimierung berücksichtigt, umfassende und effiziente Berichte erstellt sowie detaillierte Analysen für Boundary-Scan Tests bietet.