"Überall verwenden Ingenieure MATLAB und Simulink zum Entwickeln von Systemen und Algorithmen", erklärt Tom Erkkinen, Embedded Applications and Certification Manager bei MathWorks. "Mit dem HDL Coder und dem HDL Verifier müssen bei der Entwicklung von FPGA- und ASIC-Designs HDL-Code oder Test-Benches nicht mehr manuell geschrieben werden."

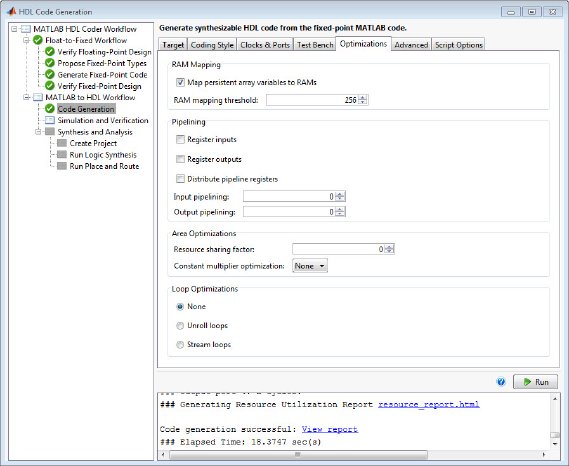

Der HDL Coder erstellt aus MATLAB-Funktionen und Simulink-Modellen portablen, synthetisierbaren VHDL- und Verilog-Code, der zur FPGA-Programmierung oder zum ASIC-Prototyping und -Design verwendet werden kann. Auf diese Weise können Ingenieur-Teams jetzt die besten Algorithmen zur Hardware-Implementierung sofort identifizieren. Aufgrund der Nachverfolgbarkeit zwischen Simulink-Modellen und generiertem HDL-Code ist weiterhin die Entwicklung von High-Integrity Anwendungen gemäß DO-254 und weiteren Standards möglich.

"HDL Coder lässt sich in die Xilinx ISE Design-Suite integrieren und ermöglicht so einen effizienten Workflow, mit dem Algorithmen-Entwickler bei Einsatz von MathWorks-Produkten Xilinx-FPGAs als Zielplattform einfach adressieren können", erläutert Vin Ratford, , Sr. Vice President Worldwide Marketing and Business Development bei Xilinx. "Diese Integration ermöglicht zudem gemeinsamen Kunden einen Zugang zu einer breiten Palette von Xilinx-optimierter IP innerhalb des HDL Coders, was die Produktivität weiter steigert."

Der HDL Verifier unterstützt jetzt auch die Verifikation mit FPGA-Hardware-in-the-Loop für Altera- und Xilinx-FPGA-Boards. HDL Verifier bietet Co-Simulationsschnittstellen, die MATLAB und Simulink mit Cadence Incisive, Mentor Graphics ModelSim und Questa HDL-Simulatoren verbinden. Mit dieser Funktionalität können Ingenieure schnell überprüfen, ob eine HDL-Implementierung mit den entsprechenden MATLAB-Algorithmen und Systemspezifikationen von Simulink übereinstimmt.

"Mit zunehmender Verbreitung von FPGAs in der Industrie benötigen Entwickler neue Methoden, um eine Brücke zwischen Systemmodellen und FPGA-Designs zu schlagen", erklärt Vince Hu, Vice President of Product and Corporate Marketing bei Altera. "Der HDL Verifier verknüpft Systemmodelle mit FPGA-Designs und ermöglicht es so Ingenieuren, Verifizierungsverfahren mittels FPGA-Hardware-in-the-Loop auf Basis von Altera-FPGAs und Simulink durchzuführen. Dieser Arbeitsablauf verkürzt Verfikationszyklen und verhilft Ingenieuren zu größerer Sicherheit bei Hardware-Implementierungen."

Preise und Verfügbarkeit:

HDL Coder und HDL Verifier sind ab sofort verfügbar. Weitere Informationen finden Sie auf den Produkt-Websites www.mathworks.com/... bzw. www.mathworks.com/....

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.